ogy, the IC occupies an extremely small die area of only  $3 \times 3 \text{ mm}^2$ . We have proposed a new low-IF transceiver architecture to simultaneously achieve both a small chip area and good minimum input sensitivity.

The distinctive point of the receiver architecture is that we replace the complicated high-order analog filter for channel selection with the combination of a simple low-order analog filter and a sharp digital band-pass filter. This architecture can eliminate large-value capacitors from the channel selection filter. We also proposed a high-speed convergence AGC and a demodulation block to realize the proposed digital architecture. The proposed AGC converges within  $6\,\mu s$ , which is fast enough for the frequency hopping access method used by Bluetooth transceivers.

For the transceiver, we reduced the chip area by applying a new form of direct modulation for the VCO. Since conventional VCO direct modulation tends to suffer from variation of the modulation index with frequency, we have developed a new compensation technique. The proposed technique can reduce the variation by one-third of the value without this technique, to less than  $\pm 1.8\%$ . We also developed a new method of biasing to improve the VCO's PSRR, and achieve a good phase-noise result, with levels below  $-128\,\mathrm{dBc/Hz}$  at a 3-MHz offset frequency.

The transceiver achieved good minimum input sensitivity of -85 dBm at the maximum bit-error rate and showed all of the interference performance that satisfied the requirements of the Bluetooth standard.

#### References

- [1] The Bluetooth Special Interest group, "The Bluetooth specification,

- [2] F. Op't Eynde, J. Schmitt, V. Charlier, R. Alexandre, C. Sturman, K. Coffin, B. Mollekens, J. Craninckx, S. Terrijn, A. Monterastelli, S. Beerens, P. Goetschalckx, M. Ingels, D. Joos, S. Guncer, and A. Pontioglu, "A fully-integrated single-chip SOC for Bluetooth," IEEE ISSCC Digest of Technical Papers, vol.44, pp.196–197, Feb. 2001.

- [3] A. Ajjikuttira, C. Leung, E. Khoo, M. Choke, R. Singh, T. Teo, B. Cheong, J. See, H. Yap, P. Leong, C. Law, M. Itoh, A. Yoshida, Y. Yoshida, A. Tamura, and H. Nakamura, "A fully-integrated CMOS RFIC for Bluetooth applications," IEEE ISSCC Digest of Technical Papers, vol.44, pp.198-199, Feb. 2001.

- [4] H. Darabi, S. Khorram, E. Chien, M. Pan, S. Wu, S. Moloudi, J.C. Leete, J.J. Real, M. Syed, R. Lee, B. Ibrahim, M. Rofougaran, and A. Rofougaran, "A 2.4 GHz CMOS transceiver for Bluetooth," IEEE ISSCC Digest of Technical Papers, vol.44, pp.200-201, Feb. 2001.

- [5] N. Filiol, N. Birkett, J. Cherry, F. Balteanu, C. Cojocaru, A. Namdar, T. Pamir, K. Sheikh, G. Glandon, D. Payer, A. Swaminathan, R. Forbes, T. Riley, S.M. Alinoor, E. MacRobbie, M. Cloutier, S. Pipilos, and T. Varelas, "A 22 mW Bluetooth RF transceiver with direct RF modulation and on-chip IF filtering," IEEE ISSCC Digest of Technical Papers, vol.44, pp.202–203, Feb. 2001.

- [6] H. Komurasaki, H. Sato, M. Ono, T. Ebana, H. Takeda, K. Takahashi, Y. Hayashi, T. Iga, K. Hasegawa, and T. Miki, "A single-chip 2.4 GHz RF transceiver LSI with a wide-range FV conversion demodulator," IEEE ISSCC Digest of Technical Papers, vol.44, pp.206-207, Feb. 2001.

- [7] P. Zeiji, J.T. Eikenbroek, P. Vervoort, S. Setty, J. Tangenberg, G. Shipton, E. Kooistra, C. Keekstra, D. Belot, K. Visser, E. Bosma, and C. Blaakmeer, "A Bluetooth radio in 0.18-\(\mu\)m CMOS," IEEE J. Solid-State Circuits, vol.37, no.12, pp.1679-1687, Dec. 2002.

- [8] G. Chang, L. Jansson, K. Wang, J. Grilo, R. Montemayor, C. Hull, M. Lane, A.X. Estrada, M. Anderson, I. Galton, and S.V. Kishore, "A direct-conversion single-chip radio-modern for Bluetooth," IEEE ISSCC Digest of Technical Papers, vol.45, pp.88–89, Feb. 2002.

- [9] J. Cheah, E. Kwek, E. Low, C. Quek, C. Yong, R. Enright, J. Hirbawi, A. Lee, H. Xie, L. Wei, L. Luong, J. Pan, S. Yang, W.F.A. Lau, and W. Ngai, "Design of a low-cost integrated 0.25

mm CMOS Bluetooth SOC in 16.5 mm<sup>2</sup> silicon area," IEEE ISSCC Digest of Technical Papers, vol.45, pp.90–91, Feb. 2002.

- [10] H. Darabi, J. Chiu, S. Khorram, H. Kim, Z. Zhou, E. Lin, S. Jiang, K. Evans, E. Chien, B. Ibrahim, E. Geronaga, L. Tran, and R. Rofougaran, "A dual mode 802.11b/Bluetooth radio in 0.35 μm CMOS," IEEE ISSCC Digest of Technical Papers, vol.46, pp.86–87. Feb. 2003.

- [11] T. Cho, D. Kang, S. Dow, C. Heng, and B. Song, "A 2.4 GHz dual-mode 0.18 μm CMOS transceiver for Bluetooth and 802.11b," IEEE ISSCC Digest of Technical Papers, vol.46, pp.88–89, Feb. 2003.

- [12] C. Cojocaru, T. Pamir, F. Balteanu, A. Namdar, D. Payer, I. Gheorghe, T. Lipan, K. Sheikh, J. Pingot, H. Paananen, M. Littow, M. Cloutier, and E. MacRobbie, "A 43 mW Bluetooth transceiver with -91 dBm sensitivity," IEEE ISSCC Digest of Technical Papers, vol.46, pp.90-91, Feb. 2003.

- [13] H. Ishikuro, M. Hamada, K. Agawa, S. Kousai, H. Kobayashi, D. Nguyen, and F. Hatori "A single-chip CMOS Bluetooth transceiver with 1.5 MHz IF and direct modulation transmitter," IEEE ISSCC Digest of Technical Papers, vol.46, pp.94–95, Feb. 2003.

- [14] M. Kokubo, M. Shida, T. Ishikawa, H. Sonoda, K. Yamamoto, T. Matsuura, M. Matsuoka, T. Endo, T. Kobayashi, K. Oosaki, T. Henmi, J. Kudoh, and H. Miyagawa, "A 2.4 GHz RF transceiver with digital channel-selection filter for Bluetooth," IEEE ISSCC Digest of Technical Papers, vol.45, pp.94–95, Feb. 2002.

- [15] M. Kokubo and S. Tanaka, "Latest topics of radio frequency transceiver circuits," Proc. 16th Circuits and Systems Workshop (Karuizawa), pp.111-116, April 2003.

- [16] M. Borremans, B. De Muer, and M. Steyaert, "The optimization of GHz integrated CMOS quadrature VCO's based on a poly-phase filter loaded differential oscillator," Proc. ISCAS, vol.2, pp.729-732, May 2000.

- [17] T. Yamawaki, M. Kokubo, K. Irie, H. Matsui, K. Hori, T. Endou, H. Hagisawa, T. Furuya, Y. Shimizu, M. Katagishi, and J.R. Hildersley, "A 2.7-V GSM RF transceiver IC," IEEE J. Solid-State Circuits, vol.32, no.12, pp.2089–2096, Dec. 1997.

- [18] T. Matsuura, J. Kudoh, and E. Imaizumi, "A 3.2-mA 6-bit pipelined A/D converter for a Bluetooth RF transceiver," IEICE Trans. Electron., vol.E85-C, no.8, pp.1538-1545, Aug. 2002.

- [19] Japanese Patent no.3029361.

Masaru Kokubo was born in Ibaraki, Japan in 1959. He received the B.S. degree in electrical engineering from the Chiba University, Chiba-shi, Japan, in 1981. Since 1981 he has been engaged in development of the analog-digital LSI, especially, the switched-capacitor filters, A/D and D/A converters for CODEC, and the digital subscriber tranceivers at the Central Research Lablatory, Hitachi Ltd., Kokubunjishi, Tokyo, Japan. His current work is in development of the transceiver ICs for PAN (Personal

Area Network) and mobile phones, and the PLLs for a micropprocessor and other ASIC applications. Mr. Kokubo is a member of IEEE. Since 2004, he is a secretary for Circuits and Systems Society Japan Chapter [CAS-04].

Masaaki Shida was born in Aichi, Japan in 1968. He received the B.E. and M.E degrees in electrical and electronic engineering and information engineering from the Nagoya University, Aichi, Japan, in 1991 and 1993, respectively. Since 1993 he has been engaged in development of the wireless communication systems at the Central Research Laboratory, Hitachi Ltd., Kokubunji-shi, Tokyo, Japan. From 2002 to 2003, he was a visiting scholar at the Center for Wireless Communications, the Uni-

versity of California, San Diego, where he worked on ultra-wideband wireless communication. He is a member of IEEE.

Takashi Oshima was born in Hiroshima, Japan in 1974. He received the B.S. degree, M.S. degree and Ph.D. in physics from Tokyo University, Tokyo, Japan, in 1996, 1998 and 2001 respectively. Since 2001 he has been engaged in the development of IF amplifiers, IF filters and transceiver architecture at the Central Research Lablatory, Hitachi Ltd., Kokubunjishi, Tokyo, Japan.

Yoshiyuki Shibahara was born in Hiroshima, Japan in 1974. He received the B.E. degree in electrical engineering and M.E. degree in information engineering from Tokyo Institute of Technology, Tokyo, Japan in 1997 and 1999 respectively. Since 1999 he has been engaged in development of clock generating circuits at the Central Research Lablatory, Hitachi Ltd., Kokubunji-shi, Tokyo, Japan.

Tatsuji Matsuura was born in Tokyo, Japan in 1952. He received the B.E. and M.E. degrees in mathematical engineering and instrumentation physics from the University of Tokyo, Tokyo, Japan, in 1976 and 1978, respectively. He joined the Central Research Lab. Hitachi, Ltd, in 1978 where he has been engaged in the research and development of analog and mixed signal signal-processing LSIs and high-speed A/D and D/A converters. Since 1995, he has been with the Semiconductor & Integrated

Circuit Group, Hitachi, Ltd., where he is a chief engineer. Since 2003, he is with Advanced Analog Technology Div. Renesas Technology Corp. He is a member of the IEEE. He served as a member of the technical program committee of the IEEE Custom Integrated Circuit Conference from 1997 to 2002.

Kazuhiko Kawai was born in Shimane, Japan in 1959. He received the B.S. degree in electrical engineering and the M.S. degree in electrical and telecommunication engineering from the University of Tohoku, Sendai, Japan, in 1982, and 1984, respectively. In 1984 he joined Semiconductor and Integrated Circuits Division, Hitachi, Ltd. Since then he has involved in the development of various analog or analog digital mixed IC for telecommunication. Currently he is with Renesas Technology Corp. where he

leads RF transceiver design team.

Takefumi Endo was born in Niigata, Japan, in 1964. He received the B.S. degree in electronic engineering from Niigata University in 1986. In 1986, he joined Hitachi Ltd. and developed a variety of analog circuits such as the AGC amplifier for CDMA, IC for subscriber line interface circuits and driver-IC for optical data link, and RFIC for GSM/PCN transceivers. Since 2000, he had been developing the RFIC for Bluetooth. Since 2003, he has engaged in development of the RFIC for Bluetooth at

Mixed Signal IC Design Dept.5, Mixed Signal IC Div., Analog & Discrete Semiconductor Business Unit, Renesas Technology Corp., Takasaki-shi, Gunma, Japan.

Katsumi Osaki was born in Gunma, Japan, in 1964. He graduated in electrical engineering from Maebashi Technical High School, Gunma, Japan and Hitachi Technical College Yokohama in 1987. In 1987, he joined Hitachi Ltd. and developed of bipolar analog and digital LSI's Since 2000, he had been developing the RFIC for Bluetooth. Since 2003, he has engaged in development of the RFIC for Bluetooth at Mixed Signal IC Design Dept.5, Mixed Signal IC Discrete Semiconductor

Business Unit, Renesas Technology Corp., Takasaki-shi, Gunma, Japan.

Hiroki Sonoda was born in Hokkaido, Japan in 1960. He received the B.A. degree in Liberal Arts from Tokyo University, Tokyo, Japan, in 1983. In 1983 he joined Semiconductor and Integrated Circuits Division, Hitachi, Ltd. Since then he has engaged in the development of various analog digital mixed ICs for consumer products. Currently he is with Renesas Technology Corp., where he pursues the embodiment of wireless communication technology.

Katsumi Yamamoto was born in Yamaguchi, Japan in 1960. He received the B.E. degree in Mechanical engineering from Sophia University in 1984. In 1984, he joined Hitachi Ltd. and developed the CODEC. Since 1987, he had been engaged in development of the Application system for Fax and Answering machine. Since 1998, he had been engaged in Marketing Support for HDD system. Since 2000, he had been developing the RFIC for Bluetooth. His current work is in System application supports

for Bluetooth at Analog & Discrete Semiconductor Business Unit, Renesas Technology Corp., Kodaira-shi, Tokyo, Japan.

Masaharu Matsuoka was born in Gunma, Japan, in 1959. In 1983, he joined Hitachi Microcomputer Engineering Ltd. he had been developing the RFIC for Bluetooth. Since 2000, he has engaged in development of the RFIC for Bluetooth at Mixed Signal IC Design Dept.5, Mixed Signal IC Div., Analog & Discrete Semiconductor Business Unit, Renesas Technology Corp., Takasaki-shi, Gunma, Japan.

Takao Kobayashi was born in Nagano, Japan in 1958. He received the B.S. electrical engineering from the Musashi institute of technology, Tokyo, Japan, in 1981. In 1981, he joined Hitachi Engineering Co., Ltd. and developed the degital signal-processing LSI. Since 1995, he has been developing the analog digital mixed IC at LSI system Dept., Hitachi Engineering Co., Ltd., Hitachi-shi, Ibaraki, Japan.

Takaaki Hemmi was born in Tokyo, Japan in 1969. He received the B.E. degree in Applied Physics and Chemistry engineering from The University of Electro-Communications in 1993. In 1993, he joined Hitachi Ltd. and developed the hardware of PHS from 1993 to 1995 in Telecommunication Systems Division. Since 1995, he had been engaged in Marketing Support for HDD system. Since 2000, he had been developing the RFIC for Bluetooth. His current work is in marketing support for Bluetooth

at Analog & Discrete Semiconductor Business Unit, Renesas Technology Corp., Chiyoda-ku, Tokyo, Japan.

Junya Kudoh received the B.Eng. degree in electronics engineering from Waseda University, Tokyo Japan in 1991. He joined Device Development Center of Hitachi, Ltd., in 1991. Currently he is Assistant Senior Engineer of Advanced Analog Development Div. of Renesas Technology Corp. and engaged in development of analog circuits. His interests include the design of analog-to-digital conversion circuits and architectures.

Hirokazu Miyagawa was born in Shiga, Japan in 1977. He received the B.S. degree in electronic engineering from Doshisha University, Kyoto, Japan in 2000. In 2000, he joined Hitachi, Ltd. He had developed RFIC for Bluetooth, engaged in development of the RFIC for Bluetooth at Mixed Signal IC Design Dept. His current work is development of the RFIC for GSM transceivers, at RFIC Business Unit, Renesas Technology Corp., Takasaki-shi, Gunma, Japan.

Hiroto Utsunomiya was born in Ehime, Japan, in 1973. In 1998, he joined Hitachi Ltd. he had been developing the RFIC for Bluetooth. Since 2000, he has engaged in development of the RFIC for Bluetooth at Mixed Signal IC Design Dept.5, Mixed Signal IC Div., Analog & Discrete Semiconductor Business Unit, Renesas Technology Corp., Takasaki-shi, Gunma, Japan.

Yoshiyuki Ezumi was born in Gunma, Japan, in 1972. In 1991, he joined Hitachi Ltd. he had been developing the RFIC for Bluetooth. Since 2000, he has engaged in development of the RFIC for Bluetooth at Mixed Signal IC Design Dept.5, Mixed Signal IC Div., Analog & Discrete Semiconductor Business Unit, Renesas Technology Corp., Takasaki-shi, Gunma, Japan.

Kunio Takayasu was born in Shimane, Japan, in 1975. He graduated from electrical engineering in Matsue National College of Technology, Shimane, Japan in 1995. Currently, he is with Front Future Corp., Takasaki-shi, Gunma, Japan. He is a digital circuitry engineer.

Jun Suzuki was born in Gunma, Japan, in 1972. In 1996, he joined Hitachi Ltd. Since 2000, he has engaged in development of the RFIC for Bluetooth at Mixed Signal IC Design Dept.5, Mixed Signal IC Div., Analog & Discrete Semiconductor Business Unit, Renesas Technology Corp., Takasaki-shi, Gunma, Japan.

Shinya Alzawa was born in Gunma, Japan, in 1968. In 1992, he joined Hitachi Ltd. he had been developing the RFIC for Bluetooth. Since 2001, he has engaged in development of the RFIC for Bluetooth at Mixed Signal IC Design Dept.5, Mixed Signal IC Div., Analog & Discrete Semiconductor Business Unit, Renesas Technology Corp., Takasaki-shi, Gunma, Japan.

Mikihiko Motoki was born in Gunma, Japan, in 1964. In 1986, he joined Hitachi Microcomputer Engineering Ltd. he had been developing the RFIC for Bluetooth. Since 2000, he has engaged in development of the RFIC for Bluetooth at Mixed Signal IC Design Dept.5, Mixed Signal IC Div., Analog & Discrete Semiconductor Business Unit, Renesas Technology Corp., Takasaki-shi, Gunma, Japan.

Yoshiyuki Abe was born in Yamagata, Japan, in 1962. In 1986, he joined Hitachi Microcomputer Engineering Ltd. and he had been engaged in development of various IC. Since 2000, he has engaged in development of the RFIC for Bluetooth at Mixed Signal IC Design Dept.5, Mixed Signal IC Div., Analog & Discrete Semiconductor Business Unit, Renesas Technology Corp., Takasaki-shi, Gunma, Japan.

Takao Kurosawa was born in Gunma, Japan, in 1962. In 1982, he joined Hitachi Microcomputer Engineering Ltd. and he had been engaged in development of various IC. Since 2000, he has engaged in development of the RFIC for Bluetooth at Mixed Signal IC Design Dept.5, Mixed Signal IC Div., Analog & Discrete Semiconductor Business Unit, Renesas Technology Corp., Takasaki-shi, Gunma, Japan.

Satoru Ookawara was born in Saitama, Japan, in 1975. In 2000, he has engaged in development of the RFIC for Bluetooth at Mixed Signal IC Design Dept.5, Mixed Signal IC Div., Fujione Techno Solutions Corp., Takasaki-shi, Gunma, Japan.

# PAPER

# A GFSK Transmitter Architecture for a Bluetooth RF-IC, Featuring a Variable-Loop-Bandwidth Phase-Locked Loop Modulator

Masaru KOKUBO<sup>†a)</sup>, Takashi OSHIMA<sup>†</sup>, Members, Katsumi YAMAMOTO<sup>††</sup>, Kunio TAKAYASU<sup>††</sup>, Yoshiyuki EZUMI<sup>††</sup>, and Shinya AIZAWA<sup>††</sup>, Nonmembers

SUMMARY The use of a two-point modulator with variable PLL loop bandwidth as a GFSK signal generator is proposed. Delta-sigma modulation is adopted for the modulator. Through the combination of a variable PLL feedback loop and delta-sigma modulation, both a fast settling time and very clear eye opening are achieved for the modulator. We fabricate it in 0.35-µm BiCMOS process technology. The two-point modulator has a center-frequency drift of only 14.9 kHz, much lower than the 178-kHz result for a single time slot in the case of direct VCO modulation. This is due to the PLL feedback loop. Evaluation also confirmed that the circuit satisfies the various characteristics required of a Bluetooth transmitter. The two-point modulator is also applicable to other transceivers which use FSK or PSK modulation, i.e. forms of modulation where a constant signal level is transmitted, and thus contributes to the simplification of a range of wireless transmitters.

key words: FSK, modulator, delta-sigma, PLL, variable loop bandwidth, Bluetooth

### 1. Introduction

The various popular forms of wireless communications include wireless LAN, the Personal Handyphone System, CDMA, GSM, and other mobile-phone standards. Personal area networks (PANs), in which the network is formed through a base station or directly among individual terminals, are now being added to this list. The Bluetooth standard for wireless communications is the best-known short-range wireless access method for the realization of PANs.

The Bluetooth standard specifies a method of communication over ranges within 10 m [1]. Bluetooth terminals will popularize direct inter-device wireless data communications for multiple items of personal equipment, and will dramatically improve the versatility and interoperability of mobile devices such as cellular phones, PDAs, and portable personal computers.

FSK (frequency-shift keying) modulation is adopted in the Bluetooth standard. In FSK, changes in frequency represent the transmitted data. Well-known ways of generating FSK signals include heterodyne modulation [2] and direct

Manuscript received July 22, 2004.

Manuscript revised October 26, 2004.

a) E-mail: m-kokubo@crl.hitachi.co.jp

DOI: 10.1093/ietele/e88-c.3.385

in-phase/quadrature (IQ) modulation [3]-[7]. Both are already in common use. When these modulation techniques are adopted in a Bluetooth transmitter, the data for transmission is initially converted to I and Q elements, which are 90° out of phase with each other. The I and Q elements are then multiplied by local carrier waves at the 2.4-GHz radio frequency in two mixers, so the results also have a phase difference of 90°. After that, to avoid the generation of image-frequency components, the outputs of the mixers are added to each other by wired-OR connections. This method generates an FSK-modulated radio-frequency wave with very small image-frequency components. Furthermore, both direct and heterodyne modulation are applicable to the realization of various kinds of modulated waves, including PSK, OPSK, and OAM.

In transceivers based on FSK modulation such as those for Bluetooth, however, these methods of modulation generate phase or frequency fluctuations according to the nonlinear characteristics of the power amplifiers, i.e. amplitude modulation is converted to phase modulation. This AM-PM problem occurs with even a small mismatch in amplitudes of the I and Q elements, and is also caused by amplitude mismatches between local carrier waves. Furthermore, we must also consider the VCO (voltage controlled oscillator) frequency-pulling problem when using direct IQ modulation. Moreover, it isn't easy to decrease power consumption in the transmitter because the modulation methods require mixers that operate in very high frequency bands, such as 2.4 GHz in the case of Bluetooth.

Direct VCO modulation is an alternative to these techniques and is used in many Bluetooth transceivers. This provides a very simple transmitter architecture that suits the generation of FSK-modulated signals. In this method, FSK signals are transmitted while the PLL (phase locked loop) is cut out to open the otherwise closed loop and the frequency-modulation signal or data for transmission is directly input to the VCO's frequency-control terminal. Of course, the PLL operates normally before transmission starts. That is, the circuit forms a closed loop and PLL frequency synthesis produces the carrier frequency for transmission.

The specified transmission bandwidth for Bluetooth is about  $\pm 500\,\mathrm{kHz}$ , and this bandwidth is wider than the loop bandwidth of a typical PLL, which is several tens of kilohertz. Therefore, generating a Bluetooth FSK modulation

<sup>&</sup>lt;sup>†</sup>The authors are with Communication Device Research Department, Central Research Laboratory, Hitachi Ltd., Kokubunjishi, 185-8601 Japan.

<sup>\*\*</sup>The authors are with Renesas Technology Corp., Takasakishi, 370-0021 Japan.

signal through the combination of a closed-loop PLL and direct VCO modulation is very difficult, because the frequency deviation is absorbed by the effect of the feedback loop of the PLL in the case of the repeated transmission of either value, i.e. "1" or "0."

A circuit for direct VCO modulation can be constructed by simply adding an analog low frequency circuit that controls the VCO control terminal to the original PLL synthesizer structure, and the circuit doesn't require the two radio frequency mixers of the direct IQ modulation method. A transceiver based on direct VCO modulation thus consumes much less power and has a smaller chip area than a transceiver based on direct IQ modulation. Direct VCO modulation is thus adopted in many transceivers [8]-[12].

Due to supply-voltage fluctuation, noise on the VCO control terminals, and the leakage current of the charge pump and other components of the PLL's loop filter, however, direct VCO modulation generally suffers from a drift in the center frequency of transmission. Since the ground and power-supply lines of a small and cheap mobile transceiver are usually far from ideal, keeping the center-frequency drift within the required frequency range (less than 25 kHz) during a single-time-slot packet-transmission period in a Bluetooth transceiver is very difficult unless feedback loops are used. Since signals are transmitted to the antenna while the PLL is open loop in direct VCO modulation, a large center-frequency drift is caused by very low levels of noise or leakage at the VCO control terminal. It isn't easy to avoid this center-frequency drift and achieve good characteristics, even when careful circuit and layout design for reduced noise is done both inside and outside the integrated

Cheah et al. [13] have proposed a closed-loop transmission method in which a frequency divider in the feedback path is controlled according to the FSK modulation signal (current state of the data). However, this method needs a compensation technique to adjust the frequency characteristics of the PLL closed-loop transfer function because the PLL loop bandwidth of the transceiver is usually much narrower than the modulation bandwidth of the Bluetooth transmitter.

Compensation of frequency characteristics at this point requires a large gain in the high-frequency range, i.e. a differentiator or HPF. Noise from the PLL will increase if we apply this technique to the transmitter. Moreover, determining the compensation characteristics isn't easy, because the loop bandwidth of the PLL readily changes due to variation in the voltage-to-frequency conversion gain of the VCO and the charge-pump current. Compensation is thus inadequate for applications that require highly precise modulation. Another example of closed-loop modulation [14] requires two DACs (digital to analog converters) for separate correction of mismatches of the VCO gain and of the charge-pump current, thus realizing precise modulation.

Two-point modulation method is well known as a method for closed-loop FSK signal generation. Filiol et al. [15] describe a two-point modulation method in which

direct VCO modulation is combined with closed-loop transmission. A premise of this form of modulation is that the modulation indices on both paths, i.e. the direct VCO modulation path and the frequency-divider modulation path in the PLL feedback loop, are equal. Two-point modulation will not operate properly when the indices are different. While two-point modulation is useful as a technique for the generation of FSK signals for Bluetooth transceivers, we must consider degradation due to the PLL loop bandwidth and drift in the center frequency of the output signal. Furthermore, while Staszewski et al. [16] have presented a method of two-point modulation that is specifically for digital signals, the method requires a means of compensation to absorb quantization noise introduced because of the restricted clock rate and a means for adjusting the DCO (digitally controlled oscillator) to maintain constant voltage-to-frequency conversion gain with varying carrier frequency.

Our proposed modulator is based on direct VCO modulation with fractional frequency divider control achieved through delta-sigma modulation. Here, we newly develop the variable loop bandwidth control technique of PLL and adopt it into the GFSK modulator for satisfying the Bluetooth specifications. The proposed new techniques reduce out-of-band frequency noise, improve the eye opening for transmitting signals, and also reduce the drift in center frequency due to noise and leakage of circuits. We have already reported on the results of simulation of the new two-point modulation architecture with a variable loop bandwidth for the PLL [17].

In this paper, we review the design methodology for the modulator and report on our integration of the full transmitter into 0.35- $\mu$ m BiCMOS and the evaluation of its performance. We demonstrate that the new architecture is effective in reducing center-frequency drift.

Design of the transmitter with a structure that allows variable loop bandwidth is described in the second section, and we report on the results of evaluation of a test chip in the third section. Finally, we conclude the paper with a brief summary as the fourth section.

# 2. Transmitter Design

The important requirements of the Bluetooth specification that apply to transmitters are listed in Table 1. Although a

Table 1 Bluetooth transmitter specifications.

| No. | Item                     |         | Bluetooth specification |  |

|-----|--------------------------|---------|-------------------------|--|

| 1   | Initial frequency offset |         | < ±25 kHz               |  |

| 2   | Center frequency drift   |         | < 25 kHz                |  |

| 3   | Frequency drift rate     |         | < 20 kHz/50 μs          |  |

| 4   | Frequency                | Average | 140 - 175 kHz           |  |

| 5   | deviation                | Minimum | > 115 kHz               |  |

| 6   | Eye-opening ratio        |         | > 0.8                   |  |

| 7   | -20-dB bandwidth         |         | < I MHz                 |  |

| 8   | In-band                  | < 2MHz  | <-20 dBm                |  |

| 9   | spurious                 | > 3MHz  | <-40 dBm                |  |

| 10  | Out-of-band spurious     |         | <-30 dBm                |  |

| _11 | PLL settling time        |         | < 220 μs                |  |

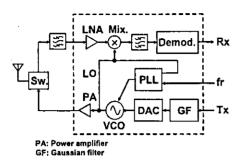

Fig. 1 Block diagram of a Bluetooth transceiver.

frequency offset of less than ±75 kHz is specified, the allowable frequency offset of a crystal oscillator for use with the transceiver is specified as less than ±20 ppm, the initial frequency offset is that listed against item 1, that is, ±25 kHz. Since noise from outside the IC will often have an effect, center frequency drift (item 2) arises because of power-supply noise on the board and so on. Items 4 to 7 are important in terms of the quality of the modulator. Item 8 indicates the extent to which in-band noise elements must be restrained so that they do not interfere with signal transfer on other Bluetooth channels. Item 9 indicates how much out-of-band noise elements have to be restrained so that they do not interfere with other (non-Bluetooth) signals. Nonlinearities of the power amplifier (PA) and VCO are usually responsible for these disturbances. A short settling time for the PLL is also desirable, since this is part of the overall time taken to transmit a frame. The settling time listed in the table is the maximum permitted with Bluetooth.

The following sections will cover construction of the proposed transmitter.

# 2.1 Transmitter Block Diagram

A block diagram of a typical Bluetooth transceiver is shown in Fig. 1. We integrated the blocks inside the area marked by the dotted line.

The transmitter of this integrated circuit consists of the GF (Gaussian filter, i.e. a filter with a Gaussian characteristic), PLL, VCO, DAC, and PA. Tx, which indicates the data sequence to be transmitted, is input to the GF. The output of the GF is converted into an analog signal by the DAC. The VCO has two control terminals, one controlled by the PLL and the other controlled by the modulating signal from the DAC so that the FM signal for transmission is generated. The PA amplifies the output of the VCO and drives an antenna when connected through the switch (Sw.).

On the receiver side, microwave signals received from the antenna are input to the integrated circuit via the switch and a band-pass filter which selects the ISM (Industrial, Science, and Medical) band at 2.4 GHz. In the first stage of the integrated circuit, the input signal is amplified by the lownoise amplifier (LNA). In the next stage, the signal is converted to an intermediate frequency by the mixer (Mix.). After that, the narrow intermediate-frequency band-pass filter

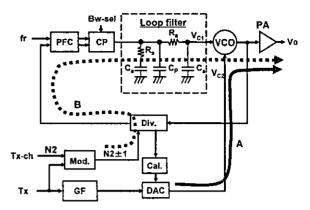

Fig. 2 Block diagram of the two-point modulation transmitter.

reduces the amplitude of disturbances potentially generated by other transceivers, selecting only the desired frequency component. Finally, the demodulator (Demod.) regenerates Rx, the received digital data. The receiver circuits of this integrated circuit have been described in a previous report [18].

### 2.2 Application of the PLL in the Transmitter Architecture

Figure 2 is a block diagram of the two-point modulator in which variable loop bandwidth is applied. The key technique is the use of a PLL synthesizer capable of fractional frequency multiplication. The two-point modulator consists of the direct VCO modulation circuit and the PLL, which includes a frequency divider (Div.). The divider is controlled by the delta-sigma modulator (Mod.), which takes the data sequence for transmission (Tx) and transmission channel information (Tx-ch) as inputs.

As stated above, the PLL is the basis of the proposed transmitter circuit. The PLL consists of a phase-frequency comparator (PFC), which compares the phase and frequency differences between the reference clock signal (fr) and the output of divider, charge-pump (CP), which converts the PFC output into an analog signal, and VCO. The loop filter between the CP and VCO consists of passive resisters and capacitors. Its role is to maintain stability and suppress noise. The current from the CP is variable. Control is provided by the signal Bw-sel, as is shown in Fig. 2.

The VCO is for two-point modulation and thus has two control terminals  $(V_{C1}, V_{C2})$ .  $V_{C1}$  is used as a conventional PLL control terminal and  $V_{C2}$  is used to apply the modulating signal, that is, the signal generated by passing Tx through the GF and DAC.

Next, Tx-ch and Tx are processed by the modulator to control the divider. TX-ch is an integer multiple N2 of the reference frequency; this selects the transmission channel of the transceiver. The modulator outputs a signal at N2 plus or minus one according to the current value of the data sequence for transmission. The maximum deviation of modulated signals from center frequencies in a Bluetooth transceiver is 0.16 MHz. Therefore, we use fractional

Fig. 3 Frequency characteristics of two-point modulation.

frequency division to generate non-integer multiples of the 1-MHz reference frequency, for example, -0.16 MHz or +0.16 MHz. The average divisor for the divider is equal to the channel number, N2. We give further details on a modulator, the so-called delta-sigma modulator, in the next sub-section.

### 2.3 Loop Bandwidth

The principle of modulation for the transmitter is now explained with the aid of Figs. 2 and 3. The transmitter has two modulation paths, the path of direct VCO control by Tx, which includes the GF and DAC (indicated by arrow A in Fig. 2) and the path for modulated divider-control of the PLL feedback loop (indicated by the dotted arrow, B, in the same figure).

After smoothing by the GF, the data for transmission is input to the DAC, which produces an analog signal  $(V_{C2})$ . This signal arrives at the VCO along path A and modulates the VCO's frequency by adjusting the value of an internal variable capacitor. Therefore, the closed-loop transfer function for direct VCO modulation from  $V_{C2}$  to  $V_O$  is given by

$$\frac{V_o(s)}{V_{C2}(s)} = \frac{1}{1 + H(s)}. (1)$$

We define the closed-loop transfer function of PLL as H(s) [19].

The frequency characteristics of H(s) are shown by the upper trace in Fig. 3. Therefore, the closed-loop transfer characteristic from the DAC output to the VCO output is the high-pass characteristic labeled A in the lower trace of Fig. 3. The cut-off frequency of the closed-loop transfer function is almost equal to the loop bandwidth,  $\omega_c$ , of H(s).

Next, Tx and Tx-ch are input to the modulator, which produces the control signal  $(N2\pm1)$  for the divider. To make the result of  $N2\times fr$  equal to the carrier frequency, the average control signal for the divider, denoted by  $N2\_avr$ , must be equal to N2. The frequency divisor for the divider is immediately updated by the control signal.

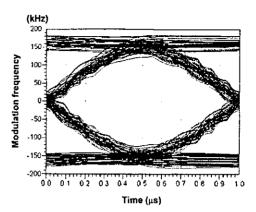

Fig. 4 Eye pattern (the PLL's loop bandwidth is 9 kHz).

The transfer function from TX to  $V_O$  is given by

$$\frac{V_o(s)}{TX} = -\frac{N2 \cdot H(s)}{1 - H(s)}.$$

(2)

In other words, the signal from the modulator has a low-pass frequency characteristic with a cut-off frequency of  $\omega_c$  (labeled B in Fig. 3). We adopted a delta-sigma modulator for the modulator. A delta-sigma modulator spreads the quantization noise E(z) into the higher-frequency range. The transfer function Y(z) of the noise processed by delta-sigma modulation is given by

$$Y(z) = E(z)(1 - z^{-1})^{N}$$

(3) [20]

Here, N is the order of the delta-sigma modulator and  $z^{-1}$  is unit delay time, which is equivalent to the sampling period of the delta-sigma modulator.

The frequency characteristic corresponding to Eq. (3) is labeled C in Fig. 3. The noise component is thus concentrated in the higher-frequency range. This noise component doesn't affect the output,  $V_O$ , because multiplication by the PLL's low-pass frequency characteristic leads to the quantization-noise response labeled D in Fig. 3.

Therefore, we can maintain the feedback loop of the PLL while generating the GFSK signal. All-pass characteristics are obtained with respect to the signal input, since the transfer function is the superposition of the low-pass and high-pass characteristics for modulation on the two transmitter paths.

The loop bandwidth,  $\omega_c$ , is an important parameter which decides the noise contribution ratio of the two paths in the output signal. In other words, the noise contribution of the direct VCO modulation path increases when  $\omega_c$  is lowered so that the PLL has a narrower loop bandwidth, and the noise contribution of the delta-sigma modulator path increases when  $\omega_c$  is raised so that the PLL has a wider loop bandwidth. The contribution of quantization noise from the delta-sigma modulator becomes larger in the latter case; that is, we know the transmitted waveform will have a lot of noise when the loop bandwidth of the PLL is wide.

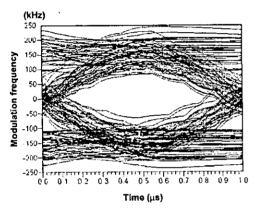

Eye patterns of the transmitted signal with three loopbandwidth values for the PLL are shown in Figs. 4, 5, and 6.

Fig. 5 Eye pattern (the PLL's loop bandwidth is 12 kHz).

Fig. 6 Eye pattern (the PLL's loop bandwidth is 17 kHz).

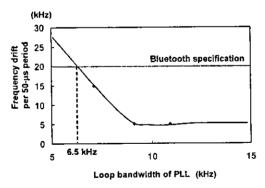

Fig.7 Frequency drift-rate: result of simulation.

For this simulation, the order N of the delta-sigma modulator was set to two, and we set  $\omega_c$  to 9 kHz in Fig. 4, 12 kHz in Fig. 5, and 17 kHz in Fig. 6. Further conditions of simulation were a large frequency drift of  $600 \, \text{Hz}/\mu\text{s}$  for the VCO, due to noise and leakage current, and a 1-MHz sampling frequency for the delta-sigma modulator.

The figures show that a wide loop bandwidth for the PLL makes it very difficult to get an output modulated wave that contains little noise.

On the other hand, too narrow a loop bandwidth means that the PLL cannot compensate for VCO frequency drift

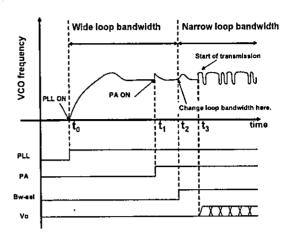

Fig. 8 Start-up procedure and VCO frequency fluctuation.

due to noise or leakage current. Results of simulation of the frequency drift rate vs. the loop bandwidth of the PLL are plotted in Fig. 7, along with the specified rate for Bluetooth. For the simulation shown in Fig. 7, we considered the noises and leakage currents occurred in PLL as the equivalent noise source at the VCO input. We measured the frequency fluctuations over the all conditions of temperature and supply voltage variations and set the VCO parameter in the simulation with the worst case drift of 600 Hz/µs. The figure clearly shows that a loop bandwidth of more than 6.5 kHz is necessary for tracking of the worst case VCO frequency drift.

# 2.4 Changing the PLL's Loop Bandwidth Over Time

The Bluetooth specification requires that the PLL have a convergence time of no more than  $220\,\mu s$ . Since a margin for stabilization must also be allowed, the PLL convergence must be complete somewhat before  $220\,\mu s$ . The settling time of a PLL is known to be a function of  $\omega_n$ , where  $\omega_n$  is the free-running frequency of the PLL [21]. We selected a loop bandwidth of about 6.5 kHz for the PLL, for the reason discussed in Sect. 2.3. Furthermore, we use a damping factor of  $\xi = 1$ . We then used Eq. (4) to get a rough estimate of settling time. The largest possible frequency hop in Bluetooth is 80 MHz and we assume a frequency error of less than 100 Hz in the steady state.

$$T = -\frac{\ln\left[\frac{\Delta f}{BW}\right]}{S\omega_n} \approx -\frac{\ln\left[\frac{100}{80 \times 10^6}\right]}{2\pi \times 6.5 \times 10^3} \approx 330 \,\mu\text{s} \tag{4}$$

The result indicates that settling within the required time period is not possible when the PLL has a narrow loop bandwidth. In this paper, we examine a technique where the loop bandwidth of the PLL is changed in multiple stages to achieve a shorter settling time.

A time chart from the point at which the Bluetooth transceiver activates the transmitter to just after the start of transmission is given as Fig. 8. The factors that significantly

obstruct convergence by a PLL are also indicated in the figure. The top plot in Fig. 8 shows the VCO's frequency of oscillation. Successively lower plots show the PLL-start signal, PA-start signal, Bw-sel (select loop-bandwidth change) signal, and Vo (Tx data transmission).

Convergence of the PLL starts when the PLL-start signal goes high  $(t_0)$ . At this time, a wide loop bandwidth is selected for the PLL, so settling is relatively fast at the beginning of convergence. In this case, we set a loop bandwidth of 40–60-kHz to obtain a settling time shorter than  $100 \,\mu s$  for the PLL. Next, the PA is activated at point  $t_1$ . Activation of the PA changes the VCO frequency by several hundreds of kilohertz, even if the PA circuit block is mounted with an independent power supply and ground line. For this reason, PLL re-convergence is required to return the VCO to the frequency assigned for transmission.

Next, after the PLL has settled such that the VCO is within a small error frequency of the assigned frequency, the loop bandwidth of the PLL is made narrower (point  $t_2$ ). However, a further very short period of re-convergence is required because of the change to the loop bandwidth, since the control signal that changes the loop bandwidth creates noise that reaches the VCO control terminals. Furthermore, the phase error of the PLL relative to the reference clock changes slightly when the loop bandwidth is changed. Therefore, if the VCO has a large frequency drift, we must include additional PLL re-convergence time for worst-case convergence conditions. Data transmission starts at  $t_3$ , that is, after the PLL output has settled at the assigned frequency. The delta-sigma modulator is also started at this point.

To determine an adequate re-convergence time for the transmitter, we measured the frequency fluctuations induced by interference in an actual integrated circuit with open-loop modulation. The VCO frequency drift rate was  $600\,\mathrm{Hz}/\mu\mathrm{s}$  and the frequency change on PA activation was  $200\,\mathrm{kHz}$ . Of course, these parameters will vary with the component tolerances, wiring layout, and so on. Therefore, our goal is to identify a margin of re-convergence time that is sufficient for use in practical design.

As a result, we selected loop-bandwidth changeover timing of  $t_1$ =80  $\mu$ s and  $t_2$ =120  $\mu$ s, and a final transmission start point of  $t_3$ =180  $\mu$ s. We confirmed that the transmitter performance in this case fulfills the Bluetooth specification, even if the loop-filter time constant, charge-pump current, and VCO voltage-to-frequency conversion gain are varied by changing component values in the integrated circuit through the full range of possible variation. The results of simulation, including initial frequency deviation  $f_0 < 10 \, \text{kHz}$ , frequency drift < 16 kHz, and eye-opening ratio > 0.95, indicate the validity of our proposed transmitter architecture. Here, we set the narrower condition of loop bandwidth for the PLL to 9 kHz, providing a margin above the 6.5-kHz minimum in consideration of manufacturing dispersal in the active and passive elements of the IC.

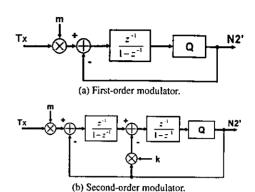

Fig. 9 Delta-sigma modulators.

#### 2.5 Modulator

We applied a delta-sigma modulator as a modulator. A block diagram of a first-order delta-sigma modulator is given as Fig. 9(a). Coefficient m is a modulation index, and in our case is multiplied by the data signal, Tx. Given the typical modulation index required by the Bluetooth specification of 0.16 and a setting of 2400 as the divisor for the divider in Fig. 2, the difference between the period of the divider output and the period of the reference clock is 69.2 ps. This value is almost equal to 1/6 (0.16666) of one period (416 ps) of the 2.4-GHz radio frequency signal used in Bluetooth. Therefore, we input Tx to the delta-sigma modulator after multiplication by m=0.16 ( $\rightleftharpoons$  1/6).

The first-order delta-sigma modulator consists of an integrator (labeled  $z^{-1}/(1-z^{-1})$ ), a quantizer (Q), which detects the polarity of the output of the integrator and outputs plus or minus one, and a subtractor, which calculates differences between the output of Q and the input.

After adjusting the delay of the output (N2') of the delta-sigma modulator to match the fixed delay of the DAC in the path from the Tx input to the  $V_{C2}$  terminal minus the set-up period required for control of the divider, closed-loop modulation is initiated by applying N2 to the divider of the PLL.

A block diagram of a second-order delta-sigma modulator is given as Fig. 9 (b). The structure differs from that of a first-order delta-sigma modulator in the inclusion of an additional subtractor, which subtracts the output of Q from the output of the first-stage integrator. Multiplication by a coefficient k before subtraction is adopted for stability. We used k=2 in our application.

The unique sequence "1010" is continuously transmitted for measurement of the center frequency in Bluetooth transmission. When this sequence is input to the first-order delta-sigma modulator, either of two output conditions is possible: continuous output of "1, 1, -1, and -1," and continuous output of "1, -1, 1, and -1." These two output patterns from the modulator are caused by differences of their initial value of the integrator of the first order delta-sigma modulator. Of course, the average frequency is the

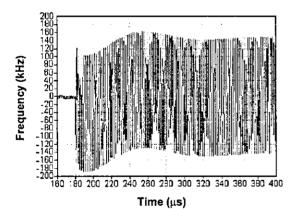

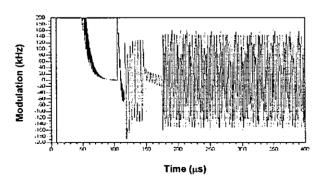

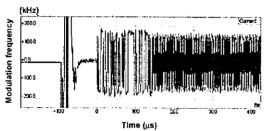

same in both cases. However, unsatisfactory frequency drift and frequency-drift rate occur when being the former condition. The simulated response of the two-point modulator when the sequence "1, 1, -1, and -1" is continuously output from the first-order delta-sigma modulator is shown in Fig. 10, where the vertical axis represents modulation frequency and the horizontal axis represents time (the transmitter is activated at  $180\,\mu s$ ). A large frequency drift of 41.5 kHz and fast frequency-drift rate of 54.2 kHz per 50- $\mu s$  period are seen under the former condition, while there is no frequency drift under the latter condition. Therefore, we conclude that adopting the first-order delta-sigma modulator into the transmitter is not adequate for Bluetooth applications.

The advantage of the second-order delta-sigma modulator in this case is that it does not output a periodical fixed pattern. However, if the center-frequency-measurement pattern specified for Bluetooth, i.e. continuous repetition of "I, 0, 1, 0," is input to the modulator, the output of the second-order delta-sigma modulator does tend to output a fixed pattern. Frequency drift occurs just after the delta-sigma modulator is activated because of the discontinuity conveyed to the PLL, and we simulate the frequency drift in this case. Fortunately, simulation shows that the second order delta-sigma modulator is effective in this application, since the re-

Fig. 10 Result of simulation for frequency drift when using first-order delta-sigma modulation.

Fig. 11 Result of simulation for frequency drift when using second-order delta-sigma modulation.

sults of simulation for frequency drift are lower than 8 kHz under all conditions.

Figure 11 shows the center-frequency drift of the transmitter with the second-order delta-sigma modulator when loop-bandwidth switching is adopted. In Fig. 11, the transmitter is activated at  $10\,\mu s$ . This simulation was done with the maximum possible frequency drift of the VCO due to leakage current and the greatest possible level of interference due to PA activation.

#### 2.6 Calibration for Two-Point Modulation

For correct operation of the two-point modulator, we must design paths A and B in Fig. 2 to have equal gain. As is shown in Fig. 2, a gain-adjustment function in the form of the calibration circuit (Cal.) was included in this IC. Fixed voltages are independently supplied to each of the control terminals,  $V_{C1}$  and  $V_{C2}$ , and the counter in the divider is used to count the VCO output. We can then estimate the error frequency through comparison with the reference clock, which is generated by a crystal oscillator.

Calibration can thus be completed in a short time by using a very simple and easy structure, with the only extra requirement being the calibration circuit. Furthermore, calibration is carried out automatically when power is supplied, and the function thus always corrects any gain imbalance between the two paths to the two-point modulator.

#### 3. Results of Transmitter Measurement

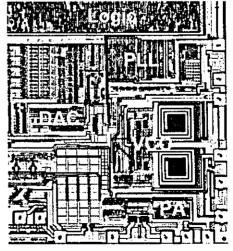

We used 0.35-µm BiCMOS technology to experimentally fabricate a transmitter based on the proposed two-point modulator technique in a Bluetooth RF-LSI. A chip photograph of the transmitter block is shown in Fig. 12.

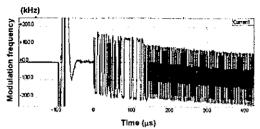

The result of frequency analysis of the transmitter output is shown in Fig. 13. The vertical axis represents the frequency deviation from the center frequency of the specified

Fig. 12 Chip photograph of the transmitter block.

(b) When the PLL is active.

Fig. 13 Transmitter center-frequency drift,

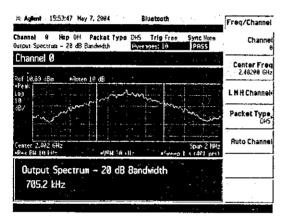

Fig. 14 Output spectrum of the transmitter.

channel and the horizontal axis represents the time relative to activation of the transmitter. Results under two measurement conditions are given in the figure: (a) operation with conventional direct VCO modulation and (b) operation with the proposed technique. The figures show the first two-thirds of a single transmission slot.

The transmitter with conventional direct VCO modulation has a center-frequency drift of 178 kHz in a single time slot (625  $\mu$ s). The new circuit reduces the center-frequency drift to 14.9 kHz. The difference is clearly visible in Fig. 13(b), demonstrating the effectiveness of the proposed modulation technique.

The transmitter's output spectrum and eye pattern are shown in Figs. 14 and 15, respectively. The measured -20-dB bandwidth of the output spectrum is 705 kHz and the eye-opening ratio is 0.87. The transmitter thus has good performance as a GFSK modulator.

Results of evaluation for the transmitter are summa-

Fig. 15 Transmitter eye pattern.

Table 2 Evaluation results.

| No. | Item                     |         | Bluetooth specification | Evaluation results |

|-----|--------------------------|---------|-------------------------|--------------------|

| l   | Initial frequency offset |         | < ±25 kHz               | -10.7 kHz          |

| 2   | Center frequency drift   |         | < 25 kHz                | 14.9 kHz           |

| 3   | Frequency drift rate     |         | < 20 kHz/50 µs          | 6.9 kHz/50µs       |

| 4   | Frequency                | Average | 140 - 175 kHz           | 164.5 kHz          |

| 5   | deviation                | Minimum | > 115 kHz               | 122.9 kHz          |

| 6   | Eye-opening ratio        |         | > 0.8                   | 0.87               |

| 7   | -20-dB bandwidth         |         | < I MHz                 | 0.705 MHz          |

| 8   | In-band                  | < 2MHz  | < -20 dBm               | -49.5 dBm          |

| 9   | spurious                 | > 3MHz  | < -40 dBm               | -53.8 dBm          |

| 10  | Out-of-band spurious     |         | < -30 dBm               | -37.8 dBm          |

| 11  | PLL settling time        |         | < 220 μs                | 180 µs             |

rized in Table 2, confirming satisfaction of all items required by the Bluetooth specification.

#### 4. Conclusions

A two-point modulator with variable PLL loop bandwidth has been proposed for use as a GFSK signal generator. The device was fabricated in 0.35- $\mu$ m BiCMOS process technology.

Delta-sigma modulation was applied in the input of the two-point modulator. During actual transmission, the delta-sigma modulator shifts quantification noise to higher frequencies; using the PLL with a narrower loop bandwidth then prevents deterioration of the eye opening at the output. On the other hand, the loop bandwidth of the PLL is set wide for fast convergence during the earliest stage of settling. The combination of these techniques in this new two-point modulator achieved both a fast settling time and very clear and well-defined eye openings.

Center-frequency drift is much lower with the proposed two-point modulator than with direct VCO modulation (14.9 kHz vs. 178 kHz, both for a single time slot). This demonstrates the effectiveness of the PLL feedback loop in reducing drift due to leakage current and noise. Furthermore, evaluation confirmed that the transmitter satisfies all of the various conditions of the Bluetooth specification.

Moreover, this two-point modulator is applicable to other transceivers in which FSK or PSK modulation is used, that is, where transmission is at a constant signal level, and thus contributes to the simplification of a wide range of wireless transmitters.

### Acknowledgments

The authors thank Mr. Yoshiyuki Shibahara of Hitachi Ltd.,

for discussions regarding transmitter circuits for Bluetooth, and Mr. Kazuhiko Kawai and his group at Renesas Technologies Corporation for the detailed design of the integrated circuit.

#### References

- The Bluetooth Special Interest Group, The Bluetooth Specification, V1.1.

- [2] B.S. Song, V. Leung, T. Cho, D. Kang, and S. Dow, "A 2.4-GHz Bluetooth transceiver in 0.18-\(\mu\)m CMOS," IEEE Proc. Asia-Pacific Conference on ASIC, pp.117-120, Aug. 2002.

- [3] H. Darabi, S. Khorran, H.M. Chien, M.A. Pan, S. Wu, S. Moloudi, J.C. Leete, J.J. Rael, M. Syed, R. Lee, B. Ibrahim, M. Rofougaran, and A. Rofougaran, "A 2.4-GHz CMOS transceiver for Bluetooth," IEEE J. Solid-State Circuits, vol.36, no.12, pp.2016–2024, Dec. 2001.

- [4] A. Zoffaghari, A. Chan, and B. Razavi, "A 2.4-GHz 34-mW CMOS transceiver for frequency-hopping and direct-sequence applications," IEEE ISSCC Digest of Tech. Papers, pp.418-419, Feb. 2001.

- [5] F.O. Eynde, J.J. Schmit, V. Charlier, R. Alexandre, C. Sturman, K. Coffin, B. Mollenkens, J. Craninckx, S. Terrin, A. Monterastelli, S. Beerens, P. Goetschalackx, M. Ingles, D. Joos, S. Guncer, and A. Pontioglu, "A fully-integrated single-chip SOC for Bluetooth," IEEE ISSCC Digest of Tech. Papers, pp.196–197, Feb. 2001.

- [6] G. Chang, L. Jansson, K. Wang, J. Grilo, R. Montemayor, C. Hull, M. Lane, A.X. Estrada, M. Anderson, I. Galton, and S.V. Kishore, "A direct-conversion single-chip radio-modem for Bluetooth," IEEE ISSCC Digest of Tech. Papers, pp.88–89, Feb. 2002.

- [7] P. Zeijl, J.W.T. Eikenbrock, P.P. Veroort, S. Setty, J. Tangenberg, G. Shipton, E. Kooistra, I.C. Keestra, D. Belot, K. Visser, E. Bosma, and S.C. Blaakmeer, "A Bluetooth radio in 0.18-μm CMOS," IEEE J. Solid-State Circuits, vol.37, no.12, pp.1679–1687, Dec. 2002.

- [8] A. Ajjikuttira, C. Leung, E.S. Khoo, M. Choke, R. Singh, T.H. Teo, B.C. Cheong, J.H. See, H.S. Yap, P.B. Leong, C.T. Law, M. Itoh, A. Yoshida, Y. Yoshida, A. Tamura, and H. Nakamura, "A fully-integrated CMOS RFIC for Bluetooth applications," IEEE ISSCC Digest of Tech. Papers, pp.198–199, Feb. 2001.

- [9] H. Ishikuro, M. Hamada, K. Agawa, S. Kousai, H. Kobayashi, D.M. Nguyen, and F. Hatori, "A single-chip CMOS Bluetooth transceiver with 1.5 MHz IF and direct modulation transmitter," IEEE ISSCC Digest of Tech. Papers, pp.94–95, Feb. 2003.

- [10] H. Komurasaki, T. Sano, T. Heima, K. Yamamoto, H. Wakada, I. Yasui, M. Ono, T. Miwa, H. Sato, T. Miki, and N. Kato, "A 1.8-V operation RF CMOS transceiver for 2.4-GHz-band GFSK applications," IEEE J. Solid-State Circuits, vol.38, no.5, pp.817–825, May 2003.

- [11] M. Ugajin, A. Yamagishi, J. Kodate, M. Harada, and T. Tsukahara, "A 1-V CMOS/SOI Bluetooth RF transceiver for compact mobile applications," Symposium on VLSI Circuits—Digest of Tech. Papers, pp.123-126, May 2003.

- [12] M. Kokubo, M. Shida, T. Ishikawa, H. Sonoda, K. Yamamoto, T. Matsuura, M. Matsuoka, T. Endo, T. Kobayashi, K. Oosaki, T. Henmi, J. Kudoh, and H. Miyagawa, "A 2.4-GHz RF transceiver with digital channel-selection filter for Bluetooth," IEEE ISSCC Digest of Tech. Papers, vol.45, pp.94-95, Feb. 2002.

- [13] J. Cheah, E.H. Kwek, E.C. Low, C.K. Quek, C. Yong, R. Enright, J. Hirbawi, A. Lee, H. Xie, L. Wei, L. Luong, J. Pan, S.T. Yang, W.F. Andy, and W.L. Ngai, "Design of a low-cost integrated 0.25-μm CMOS Bluetooth SOC in 16.5-mm<sup>2</sup> silicon area," IEEE ISSCC Digest of Tech. Papers, pp.90–91, Feb. 2002.

- [14] S. Pamarti, L. Jansson, and I. Galton, "A wideband 2.4-GHz deltasigma fractional-N PLL with 1-Mb/s in-loop modulation," IEEE J. Solid-State Circuits, vol.39, no.1, pp.49-62, Jan. 2004.

- [15] N. Filiol, N. Birkett, J. Cherry, F. Baltanu, C. Cojocaru, A. Namdar,

- T. Pamir, K. Sheikh, G. Glandon, D. Payer, A. Swaminathan, R. Forbes, T. Riley, S.M. Alinoor, E. Macrobie, M. Cloutier, S. Pipilos, and T. Varelas, "A 22-mW Bluetooth RF transceiver with direct RF modulation and on-chip filtering," IEEE ISSCC Digest of Tech. Papers, pp.202–203, Feb. 2001.

- [16] R.B. Staszewski, C.M. Hung, K. Maggio, J. Wallberg, D. Leipold, and P.T. Balsara, "All-digital phase-domain TX frequency synthesizer for Bluetooth radios in 0.13-μm CMOS," IEEE ISSCC Digest of Tech. Papers, pp.272–273, Feb. 2004.

- [17] T. Oshima and M. Kokubo, "Two-point modulation transmitter with variable loop bandwidth," IEICE Technical Report, ICD2004-54, July 2004.

- [18] M. Kokubo, M. Shida, T. Oshima, Y. Shibahara, T. Matsuura, K. Kawai, T. Endo, K. Osaki, H. Sonoda, K. Yamamoto, M. Matsuoka, T. Kobayashi, T. Hemmi, J. Kudoh, H. Miyagawa, H. Utsunomiya, Y. Ezumi, K. Takayasu, J. Suzuki, S. Aizawa, M. Motoki, Y. Abe, T. Kurosawa, and S. Ookawara, "A small-chip-area transceiver IC for Bluetooth featuring a digital channel-selection filter," IEICE Trans. Electron., vol.E87-C, no.6, pp.878-887, June 2004.

- [19] A. Hajimiri, "Noise in phase-locked loops," IEEE SSMSD Southwest Symposium on Mixed-Signal Design, pp.1-6, Feb. 2001.

- [20] P.M. Aziz, H.V. Sorensen, and J. van der Spiegel, "An overview of sigma-delta converters," IEEE Signal Process. Mag., vol.13, no.1, pp.61-84, Jan. 1996.

- [21] B. Razavi, Design of Analog CMOS Integrated Circuits, McGraw-Hill, 2001.

Masaru Kokubo was born in Ibaraki, Japan in 1959. He received the B.S. degree in electrical engineering from the Chiba University, Chiba-shi, Japan, in 1981. Since 1981 he has been engaged in development of analog-digital LSIs, especially, switched-capacitor filters, the A/D and D/A converters for CODEC, and the digital subscriber tranceiver at the Central Research Lablatory, Hitachi Ltd., Kokubunji-shi, Tokyo, Japan. His current work is in development of PAN (Personal Area Network)

transceivers, mobile phones RF-ICs for GSM standards, and PLLs for microprocessors and the other SoC applications. Mr. Kokubo is a member of IEEE. Since 2004, he is a secretary for Circuits and Systems Society Japan Chapter of IEEE and also the sub-committee member of ISSCC and ESSCIRC.

Takashi Oshima was born in Hiroshima, Japan in 1974. He received the B.S. degree, M.S. degree and Ph.D. in physics from Tokyo University, Tokyo, Japan, in 1996, 1998 and 2001 respectively. Since 2001 he has been engaged in the development of IF amplifiers, IF filters and transceiver architecture at the Central Research Lablatory, Hitachi Ltd., Kokubunjishi, Tokyo, Japan.

Katsumi Yamamoto was born in Yamaguchi, Japan in 1960. He received the B.E. degree in Mechanical engineering from Sophia University in 1984. In 1984, he joined Hitachi Ltd. and developed the CODEC. Since 1987, he had been engaged in development of the Application system for Fax and Answering machine. Since 1998, he had been engaged in Marketing Support for HDD system. Since 2000, he had been developing the RFIC for Bluetooth. His current work is in development of Power man-

agement IC in Renesas Technology Corp.

Kunio Takayasu was born in Shimane, Japan, in 1975. He graduated from electrical engineering in Matsue National College of Technology, Shimane, Japan in 1995. Currently, he is with Renesas Technology Corp., Takasaki-shi, Gunma, Japan. He is a digital circuitry engineer.

Yoshiyuki Ezumi was born in Gunma, Japan, in 1972. In 1991, he joined Hitachi Ltd. he had been developing the RFIC for Bluetooth. Since 2000, he has engaged in development of the RFIC for Bluetooth at Mixed Signal IC Design Dept.2, Mixed Signal IC Div., Analog & Discrete Semiconductor Business Unit, Renesas Technology Corp., Takasaki-shi, Gunma, Japan.

Shinya Aizawa was born in Gunma, Japan, in 1968. In 1992, he joined Hitachi Ltd. he had been developing the RFIC for Bluetooth. Since 2001, he has engaged in development of the RFIC for Bluetooth at Mixed Signal IC Design Dept.2, Mixed Signal IC Business Unit, Standard Product Business Group, Renesas Technology Corp., Takasaki-shi, Gunma, Japan.

# Overexpression of Inducible Nitric Oxide Synthase in Rostral Ventrolateral Medulla Causes Hypertension and Sympathoexcitation via an Increase in Oxidative Stress

Yoshikuni Kimura, Yoshitaka Hirooka, Yoji Sagara, Koji Ito, Takuya Kishi, Hiroaki Shimokawa, Akira Takeshita, Kenji Sunagawa

Abstract—The present study examined the role of inducible nitric oxide synthase (iNOS) in the rostral ventrolateral medulla (RVLM) of the brain stem, where the vasomotor center is located, in the control of blood pressure and sympathetic nerve activity. Adenovirus vectors encoding iNOS (AdiNOS) or  $\beta$ -galactosidase (Ad $\beta$ gal) were transfected into the RVLM in Wistar-Kyoto (WKY) rats. Blood pressure and heart rate were monitored using a radiotelemetry system. iNOS expression in the RVLM was confirmed by immunohistochemical staining or Western blot analysis. Mean arterial pressure significantly increased from day 6 to day 11 after AdiNOS transfection, but did not change after Adβgal transfection. Urinary norepinephrine excretion was significantly higher in AdiNOS-transfected rats than in Ad\u00bbgaltransfected rats. Microinjection of aminoguanidine or S-methylisothiourea, iNOS inhibitors, or tempol, an antioxidant, significantly attenuated the pressor response evoked by iNOS gene transfer. The levels of thiobarbituric acid-reactive substances, a marker of oxidative stress, were significantly greater in AdiNOS-transfected rats than in Adßgaltransfected rats. Dihydroethidium fluorescence in the RVLM was increased in AdiNOS-transfected rats. In addition, nitrotyrosine-positive cells were observed in the RVLM only in AdiNOS-transfected rats. Intracisternal infusion of tempol significantly attenuated the pressor response and the increase in the levels of thiobarbituric acid-reactive substances induced by AdiNOS transfection. These results suggest that overexpression of iNOS in the RVLM increases blood pressure via activation of the sympathetic nervous system, which is mediated by an increase in oxidative stress. (Circ Res. 2005;96:252-260.)

Key Words: nitric oxide synthase ■ blood pressure ■ sympathetic nervous system ■ oxidative stress ■ gene transfer

Nitric oxide (NO) in the central nervous system (CNS), including the brain stem and hypothalamus, plays an important role in the regulation of blood pressure via the sympathetic nervous system.<sup>17</sup> In general, NO in the CNS inhibits sympathetic nerve activity, thereby reducing blood pressure.<sup>2-4</sup> The rostral ventrolateral medulla (RVLM) in the brain stem contains sympathetic premotor neurons responsible for maintaining the tonic excitation of sympathetic preganglionic neurons involved in cardiovascular regulation.<sup>8-10</sup> The functional integrity of the RVLM is essential for the maintenance of basal vasomotor tone, and RVLM abnormalities might be related to the pathophysiology of hypertension<sup>11-14</sup> and heart failure.<sup>15,16</sup>

Recently, we developed a technique for adenovirusmediated endothelial NO synthase (eNOS) gene transfer into the RVLM<sup>11,14,17–19</sup> or the nucleus tractus solitarii (NTS)<sup>20,21</sup> in vivo. An increase in NO production in the RVLM induced by eNOS overexpression decreases blood pressure and heart rate (HR) by inhibiting the sympathetic nervous system.<sup>11,14,19</sup> In that series of studies, we used eNOS instead of neuronal NO synthase (nNOS), which is normally abundant in the CNS, because the purpose of the study was to examine the effect of an increase in NO production in the RVLM on cardiovascular function. There are three types of NOS: eNOS, nNOS, and inducible NOS (iNOS), eNOS and nNOS are constitutively expressed, but iNOS is expressed only during pathophysiological states such as hypertension, heart failure, and endotoxin shock, and in aging, <sup>22-28</sup>

The aim of the present study was to examine the effect of iNOS overexpression in the RVLM on blood pressure in vivo and to determine whether an increase in oxidative stress in the RVLM is involved in blood pressure changes. For this purpose, we transfected adenovirus encoding the iNOS gene (AdiNOS) into the RVLM and monitored mean arterial pressure (MAP) and HR using a radiotelemetry system in awake rats. NO activity is determined by the balance of NO and reactive oxygen species production.<sup>23</sup> Therefore, thiobarbituric acid–reactive substances (TBARS) in the RVLM were measured as an indirect marker of oxidative stress,<sup>29,30</sup> and tempol, a superoxide dismutase mimetic,<sup>29,30</sup> was microin-

Original received July 26, 2004; revision received November 9, 2004; accepted November 29, 2004.

From the Department of Cardiovascular Medicine, Kyushu University Graduate School of Medical Sciences, Fukuoka, Japan.

Correspondence to Yoshitaka Hirooka, MD, PhD, FAHA, Department of Cardiovascular Medicine, Kyushu University Graduate School of Medical

Sciences, 3-1-1 Maidashi, Higashi-ku, Fukuoka 812-8582, Japan. E-mail hyoshi@cardiol.med.kyushu-u.ac.jp

© 2005 American Heart Association, Inc.

jected bilaterally into the RVLM after transfection of AdiNOS.

### Materials and Methods

# General Procedures and In Vivo Gene Transfer Into the RVLM

The present study was approved by the Committee on Ethics of Animal Experiments, Faculty of Medicine, Kyushu University, and conducted according to the Guidelines for Animal Experiments of the Faculty of Medicine, Kyushu University. Male Wistar-Kyoto (WKY) rats (280 to 300 g, 16 to 20 weeks old) were used. Rats were obtained from an established colony at the Animal Research Institute of Kyushu University Faculty of Medicine (Fukuoka, Japan). Details of the general procedures of transfection of adenovirus vectors are available in the online data supplement at http://circres.ahajournals.org.

### Construction of Adenovirus Vectors

We used adenoviral vectors encoding the bacterial  $\beta$ -galactosidase gene, mouse iNOS gene,<sup>31,32</sup> or bovine endothelial NOS (eNOS) gene (see online data supplement for details).<sup>19,33</sup>

# Analysis of Gene Expression for $\beta$ -Galactosidase or iNOS

At day 7 after gene transfer,  $\beta$ -galactosidase expression was confirmed by staining with X-Gal in phosphate buffered saline as described previously. We performed double-immunohistochemical staining for iNOS and phenylethanolamine-N-methyltransferase (PNMT)<sup>19</sup> or nitrotyrosine. Details of the methods of immunohistochemistry are available in the online data supplement.

# Western Blot Analysis for iNOS

To confirm the local overexpression of iNOS in the RVLM, Western blot analysis for iNOS protein from tissue containing the injection sites of the RVLM obtained using the micropunch technique<sup>19</sup> was performed at day 0, 3, 5, 7, 9, 11, or 14 after the gene transfer. The procedure for Western blot analysis of RVLM tissues was described previously (see online data supplement for details).<sup>11,19</sup>

### Microinjection Into the RVLM

To confirm that changes in MAP and HR induced by AdiNOS transfection were the result of an increase in iNOS protein, we microinjected aminoguanidine (2.5 mmol/L, 50 nL per site, 250 pmol) or S-methylisothiourea (SMT; 2.5 mmol/L, 50 nL per site, 250 pmol) bilaterally into the RVLM at day 7 after transfection with AdBgal or AdiNOS. All injections were performed in rats anesthetized with sodium pentobarbital (50 mg/kg, IP followed by 20 mg/kg per hour, IV). A nonselective NOS inhibitor, No-monomethyl-Larginine (L-NMMA), was also microinjected bilaterally into the RVLM. We microinjected L-arginine, a precursor of NO. (70 mmol/L, 50 nL per site, 7 nmol) bilaterally into the RVLM at day 7 after transfection with Adßgal or AdiNOS. To examine whether the generation of superoxide anions is involved in blood pressure alteration induced by AdiNOS transfection, microinjection of tempol, a superoxide dismutase mimetic, was performed bilaterally into the RVLM (see online data supplement for details).

### Microdialysis and Measurement of NO Metabolites

We measured NO production in the RVLM as nitrite/nitrate (NOx) with in vivo microdialysis before and at day 7 after gene transfer, as described previously (see online data supplement for details).<sup>21,34,35</sup>

# Measurement of MAP, HR, and Urinary Norepinephrine Excretion

A UA-10 telemetry system (Data Sciences International) was used to measure MAP and HR. We measured urinary norepinephrine excretion for 24 hours before the gene transfer and at day 7 after the gene transfer (see online data supplement for details).

# Evaluation of Oxidative Stress in the RVLM

The RVLM tissues were homogenized in 1.15% KCl (pH 7.4), and 0.4% sodium dodecyl sulfate, 7.5% acetic acid adjusted to p 3.5 with NaOH, and 0.3% thiobarbituric acid were added to the homogenate. The amount of TBARS was determined by absorbance with a molecular extinction coefficient of 156 000 and expressed as  $\mu$ mol/g wet weight, as described previously (see online data supplement for details).<sup>30</sup> Brain superoxide anion levels were estimated in two groups of rats (AdiNOS-transfected rat, n=5; nontreated, n=5) using dihydroethidium (DHE) staining following procedures used in previous studies (see online data supplement for details).<sup>36,37</sup>

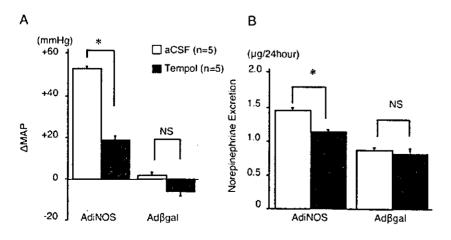

# Continuous Intracisternal Infusion Experiments With Tempol

The rats were randomly divided into four groups. Two of the groups were transfected with AdiNOS and two of the groups with Ad $\beta$ gal. Either vehicle (artificial cerebrospinal fluid, aCSF) or tempol (12  $\mu$ mol/d) were continuously infused intracisternally (0.25  $\mu$ L/h) for I week with an osmotic minipump (Alzet model 1002; DURECT Corporation), as described previously (see online data supplement for details). 38,39 Half of the animals in each transfection group were infused with vehicle and the other half were infused with tempol, producing four groups of animals: AdiNOS-VEH, AdiNOS-tempol, Ad $\beta$ gal-VEH, and Ad $\beta$ gal-tempol.

#### Statistical Analysis

All values are expressed as mean  $\pm$  SEM. Two-way ANOVA was used to compare MAP, HR, and NOx levels between the AdiNOS-treated group and the other groups. Comparisons between any two mean values were performed using Bonferroni's correction for multiple comparisons. A paired t test was used to compare 24-hour urinary norepinephrine excretion before and at day 7 after the gene transfer. A level of P < 0.05 was considered to be significant.

### Results

# Analysis of $\beta$ -Galactosidase, iNOS, or Nitrotyrosine Expression

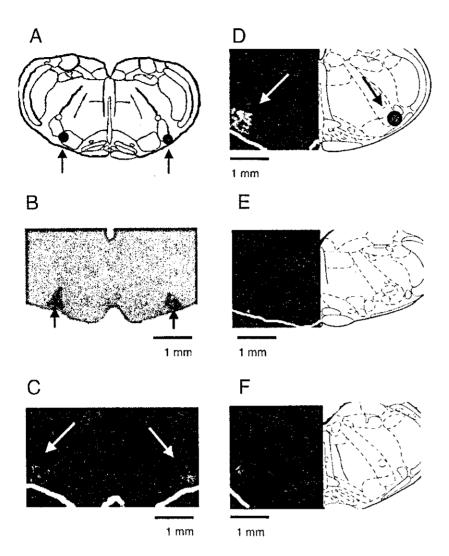

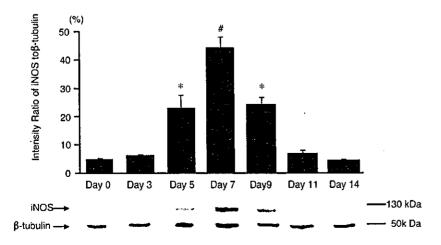

Figure 1B shows the  $\beta$ -galactosidase staining in a section of the rat brain medulla at day 7 after the gene transfer. A schematic representing injection site is shown in Figure 1A.  $\beta$ -galactosidase staining was noted in the RVLM, where Ad $\beta$ gal had been microinjected. There were no X-Galpositive cells in the adjacent brain regions. In the AdiNOS-transfected rats, the expression of iNOS protein was observed locally in the RVLM, where the AdiNOS had been transfected. Figures 1D, 1E, and 1F show the expression of iNOS in the RVLM at day 7 after the gene transfer by immunohistochemistry. Some of the C1 neurons labeled with the PNMT antibody were also detected with the anti-iNOS antibody (Figure 1C). The expression level of iNOS peaked at day 7 after the gene transfer and thereafter declined over time as detected by Western blot analysis (Figure 2).

# Microdialysis and Measurement of NO Metabolites

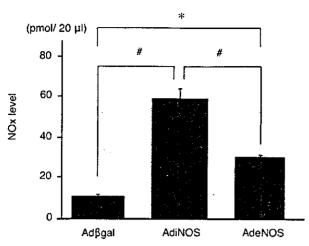

We measured the production of NO in the RVLM as NOx using in vivo microdialysis before and after gene transfer. The level of NOx was significantly higher in rats transfected with AdiNOS or AdeNOS at day 7 (AdiNOS,  $58.8\pm1.2$  or AdeNOS,  $29.4\pm1.0$  pmol/20  $\mu$ L, n=6 for each) than in Ad $\beta$ gal-treated rats ( $8.2\pm0.4$  pmol/20  $\mu$ L, n=6; Figure 3). NOx levels in AdiNOS-transfected rats were also significantly higher than in AdeNOS-transfected rats (P<0.05).

Figure 1. A, Schematic drawing of a section that includes the RVLM. Arrows indicate the RVLM. B, Site-specific expression of  $\beta$ -galactosidase by X-Gal staining at day 7 after gene transfer. C, Site-specific expression of PNMT by immunohistochemistry. D, Site-specific expression of iNOS protein by immunohistochemistry at day 7 after gene transfer. E, 0.5-mm rostral from the section as shown in D; F, 0.5-mm caudal from the section as shown in D. Arrows indicate the RVLM. Immunohistochemical staining for iNOS (green, visualized with fluorescein isothiocyanate-conjugated fluoroprobe) (D, E, and F) and PNMT (red, visualized with rhodamine-conjugated fluoroprobe) (C).

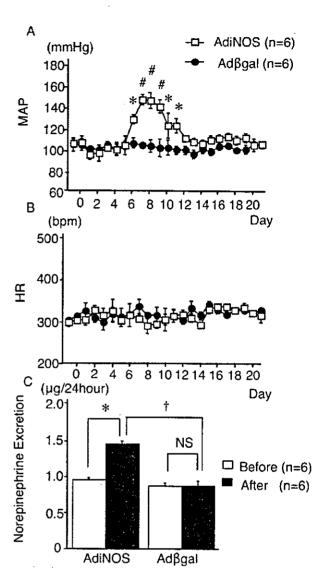

MAP, HR, and Urinary Norepinephrine Excretion Figure 4A and 4B show the changes in MAP and HR before and after the gene transfer into the RVLM. MAP was significantly increased in the AdiNOS-transfected rats between days 6 and 11 after the gene transfer (+56±14 mm Hg at day 7 after the gene transfer; P < 0.05, n = 6). In contrast, MAP did not change in the Ad $\beta$ gal-transfected rats. Injection

of AdiNOS 1 mm caudal to the RVLM also did not alter MAP. HR was not altered in either group (Figure 4B). Urinary norepinephrine excretion measured at day 7 after the gene transfer was significantly increased in the AdiNOStransfected rats relative to that measured before gene transfer (Figure 4C). Urinary norepinephrine did not change in the Ad $\beta$ gal-transfected rats (Figure 4C).

Figure 2. Representative Western blot analysis demonstrating the expression of iNOS protein, in the medulla containing the RVLM. Densitometric average was normalized to the values obtained from the analysis of  $\beta$ -tubulin (n=5 for each). \*P<0.05 vs day 0. #P<0.01 vs day 0.

**Figure 3.** Effects of transfection of Adβgal (n=6), AdiNOS (n=6), and AdeNOS (n=6) into RVLM on NOx release in dialysate of the RVLM. Basal NOx levels in AdiNOS-transfected rats were significantly higher than those in Adβgal- or AdeNOS-transfected rats. Basal NOx levels in AdeNOS-transfected rats were also significantly higher than in Adβgal-transfected rats. All data are expressed as amount of NOx in 20  $\mu$ L dialysate of RVLM. #P<0.01 compared with values of AdiNOS-transfected rats. \* $^{*}P$ <0.05 compared with values of Adβgal-transfected rats.

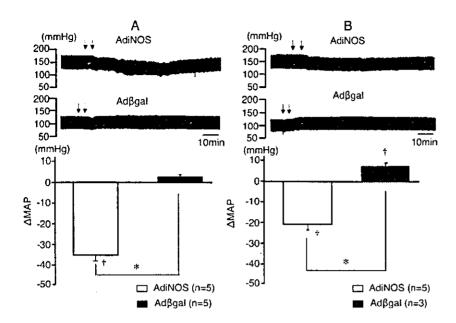

# Microinjection of NOS Inhibitors Into the RVLM

Microinjection of aminoguanidine into the RVLM at day 7 after the gene transfer produced a gradual decrease in MAP in the AdiNOS-transfected rats (Figure 5A). The maximum decrease in MAP evoked by aminoguanidine was  $-38\pm12$  mm Hg ( $P\!<\!0.05,\,n\!=\!5$ ). In contrast, microinjection of aminoguanidine did not alter MAP in the Adßgaltransfected rats (6 $\pm4$  mm Hg,  $P\!<\!0.05,\,n\!=\!5$ ). Microinjection of SMT also decreased MAP in the AdiNOS-transfected rats ( $-42\pm12$  mm Hg,  $n\!=\!5$ ). Microinjection of L-NMMA also decreased MAP in AdiNOS-transfected rats (Figure 5B), but the change was smaller than that evoked by microinjection of aminoguanidine or SMT. In contrast, L-NMMA elicited a small but significant increase in MAP in Adßgal-transfected rats ( $P\!<\!0.05,\,n\!=\!3$ ; Figure 5B).

### Microiniection of L-Arginine Into the RVLM

Microinjection of L-arginine into the RVLM at day 7 after the gene transfer produced a gradual decrease in MAP in the AdiNOS-transfected rats. The maximum decrease in MAP evoked by L-arginine was  $-35\pm6$  mm Hg (n=5).

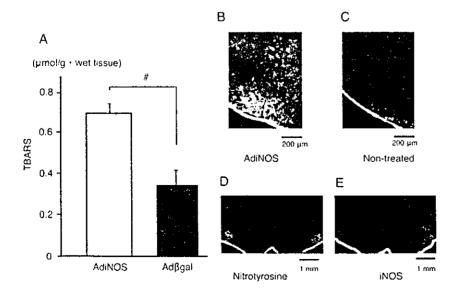

# Oxidative Stress in the RVLM After Gene Transfer

TBARS levels were significantly higher in the RVLM of AdiNOS-transfected rats than in Ad $\beta$ gal-transfected rats (Figure 6A). In AdeNOS-transfected rats, TBARS levels did not differ from those of Ad $\beta$ gal-transfected rats (AdeNOS, 0.32 $\pm$ 0.03 versus Ad $\beta$ gal, 0.29 $\pm$ 0.05  $\mu$ mol/g, n=5 for each). Figure 6B and 6C show representative images of DHE-treated brain slices from the RVLM. Increased fluorescence, representing higher superoxide anion levels, was present in the brain slices from AdiNOS- transfected rats (Figure 6B) compared with nontreated rats (Figure 6C). Some of the iNOS-positive cells were also detected with the

Figure 4. A and B, Time course of MAP (A, in mm Hg) and HR (B, in bpm) in Ad $\beta$ gal-transfected rats and AdiNOS-transfected rats before and after gene transfer. \*P<0.05 vs the values between the two groups. \*#<0.01 vs the values between the two groups. C, Urinary norepinephrine excretion for 24 hours (\$\mu\$g) before and at day 7 after the gene transfer in AdiNOS-transfected rats and Ad $\beta$ gal-transfected rats. \*#<0.05 vs Ad#gal-transfected rats. Data are shown as mean ±SEM (n=6 per group).

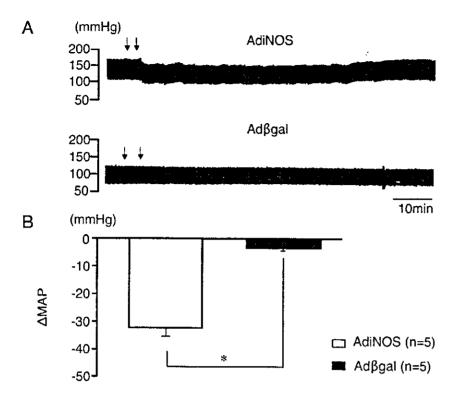

anti-nitrotyrosine antibody (Figure 6D and 6E). Microinjection of tempol elicited a depressor response in the AdiNOS-transfected rats, but not in the  $Ad\beta$ gal-transfected rats (Figure 7).

# Effect of Continuous Intracisternal Infusion With Tempol